SOAL 10.12 Buatkanlah rangkaian simulasi menggunakan IC JK Flip Flop TTL.

2. Komponen [back]

The JK Flip Flop is basically a gated RS flip flop with the addition of the clock input circuitry. When both the inputs S and R are equal to logic “1”, the invalid condition takes place. Thus to prevent this invalid condition, a clock circuit is introduced. The JK Flip Flop has four possible input combinations because of the addition of the clocked input. The four inputs are “logic 1”, ‘logic 0”. “No change’ and “Toggle”.

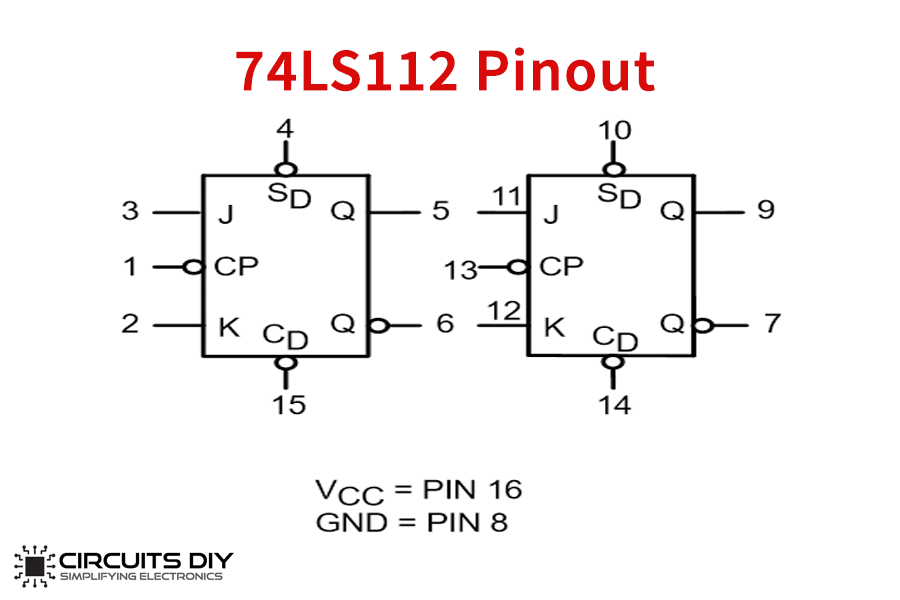

74LS112 Pinout

74LS112 Pin Configuration

Pin No Pin Name Description 1 1CLK Clock Input 1 2 1K Input Pin K1 3 1J Input Pin J1 4 1PRE’ Active low Preset Pin 1 5 1Q Output pin Q1 6 1Q’ Active Low output Pin Q1 7 2Q’ Active Low output Pin Q2 8 GND Ground Pin 9 2Q Output pin Q2 10 2PRE’ Active low Preset Pin 2 11 2J Input Pin J2 12 2K Input Pin K2 13 2CLK Clock Input 2 14 2CLR’ Active low clear/Reset pin 2 15 1CLR’ Active low clear/Reset pin 1 16 Vcc Chip Supply Voltage

| Pin No | Pin Name | Description |

|---|---|---|

| 1 | 1CLK | Clock Input 1 |

| 2 | 1K | Input Pin K1 |

| 3 | 1J | Input Pin J1 |

| 4 | 1PRE’ | Active low Preset Pin 1 |

| 5 | 1Q | Output pin Q1 |

| 6 | 1Q’ | Active Low output Pin Q1 |

| 7 | 2Q’ | Active Low output Pin Q2 |

| 8 | GND | Ground Pin |

| 9 | 2Q | Output pin Q2 |

| 10 | 2PRE’ | Active low Preset Pin 2 |

| 11 | 2J | Input Pin J2 |

| 12 | 2K | Input Pin K2 |

| 13 | 2CLK | Clock Input 2 |

| 14 | 2CLR’ | Active low clear/Reset pin 2 |

| 15 | 1CLR’ | Active low clear/Reset pin 1 |

| 16 | Vcc | Chip Supply Voltage |

74LS112 Features & Specifications

- Technology Family: LS

- Dual JK Flip Flop Package IC

- VCC (Min): 4.75V

- VCC (Max): 5.25

- Bits (#): 2

- Operating Voltage (Nom): 5V

- Frequency at normal voltage (Max): 35MHz

- Propagation delay (Max): 20ns

- IOL (Max): 8mA

- IOH (Max):-0.4mA

- Rating: Catalog

- Available in 16-pin PDIP, GDIP, PDSO packages

Applications

- PCs and notebooks

- Digital Electronics

- Shift Registers

Gerbang Logika OR (IC 7432)

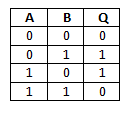

Gerbang Logika OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran 1 jika salah satu dari Masukan bernilai Logika 1 dan apabila pada gerbang OR menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

Tabel kebenaran pada tabel diatas menggambarkan fungsi OR inklusi. Gerbang OR memilki keluaran (ouput) bernilai RENDAH bila semua masukan (input) adalah bernilai RENDAH. Kolom keluaran pada tabel memperlihatkan bahwa hanya baris 1 pada tabel kebenaran OR yang menimbulkan keluaran 0, sedangkan semua baris lain menimbulkan keluaran 1.

Gerbang Logika XOR ( IC 4030)

Gerbang Ex-OR adalah kombinasi dari gerbang-gerbang logika yang komplek yang digunakan untuk membentuk rangkaian logika aritmatika, komparator dan rangkaian untuk mendeteksi error.

Gerbang logika Ex-OR disimbolkan seperti pada gambar berikut ini.

Dalam bentuk aljabar Boolean, logika Ex-OR dapat dituliskan seperti berikut ini.rumus exor :

Gerbang logika Ex-OR biasanya digunakan untuk membuat rangkaian operasi aritmatika dan perhitungan khusus Adder dan Half-Adder. Gerbang logika Ex-OR dapat berfungsi sebagai “carry-bit” atau sebagai kontroller inverter, di mana salah satu input melewatkan data biner dan input lainnya berfungsi sebagai pemberi signal kontrol.

IC gerbang logika Ex-OR antara lain :

IC TTL seri 74LS86 Quad 2 input Ex-OR

IC CMOS seri 4030 Quad 2 input EX-OR

Logic State

status logika Pengertian logis, benar atau salah, dari sinyal biner yang diberikan. Sinyal biner adalah sinyal digital yang hanya memiliki dua nilai yang valid. Dalam istilah fisik, pengertian logis dari sinyal biner ditentukan oleh level tegangan atau nilai arus sinyal, dan ini pada gilirannya ditentukan oleh teknologi perangkat. Dalam sirkuit TTL, misalnya, keadaan sebenarnya diwakili oleh logika 1, kira-kira sama dengan +5 volt pada garis sinyal; logika 0 kira-kira 0 volt. Tingkat tegangan antara 0 dan +5 volt dianggap tidak ditentukan.

Step 3: BUAT SIMULASI PADA PROTEUS

D Flip Flop

Prinsip kerja dari rangkaian Data flip-flop dengan clock diatas adalahsebagai berikut.

Apabila input clock berlogika 1 “High” maka input pada jalur data akan di teruskan ke rangkaian RS flip flop, dimana pada saat input jalur Data 1 “High” maka kondisi tersebut adalah Set Q menjadi 1 “High” dan pada saat jalur Data diberikan input 0 “Low” maka kondisi yang terjadi adala Reset Q menjadi 0 “Low”.

Kemudian Pada saat input Clock berlogika rendah maka data output pada jalur Q akan ditahan (memori 1 bit) walaupun logika pada jalur input Data berubah. Kondisi inilah yang disebut sebagai dasar dari memor 1 bit.

J-K Flip Flop

JK Flip Flop adalah salah satu macam Flip Flop yang paling banyak diguankan dalam praktik.

Pada Flip Flop ini terdapat 3 buah input yaitu J, K dan CL, J dan K berfungsi sebagai pengendali ,

jika J = 0 dan K = 0 maka output Q akan tetap seperti keadaan semula walaupun input CL berubah-ubah.

jika J = 1 dan K = 0 , maka output Q akan di set (1) pada saat pulsa CL input bergerak dari 1 ke 0.

Jika J = 0 dan K = 1 maka output Q akan reset (0) pada saat pulsa CL input bergerak dari 1 ke 0.

Tetapi jika J = 1 dan K = 1 maka JK FlipFlop akan berfungsi sebagai T Flip Flop yaitu output akan berubah Jika CL bergerak dari 1 ke 0 . Hal ini bisa dikatakan Toggle.

JK Flip Flop adalah salah satu macam Flip Flop yang paling banyak diguankan dalam praktik.

Tidak ada komentar:

Posting Komentar