Laporan Akhir II (Percobaan T flip flop)

DAFTAR ISI

4. Prinsip Rangkaian

5. Analisa

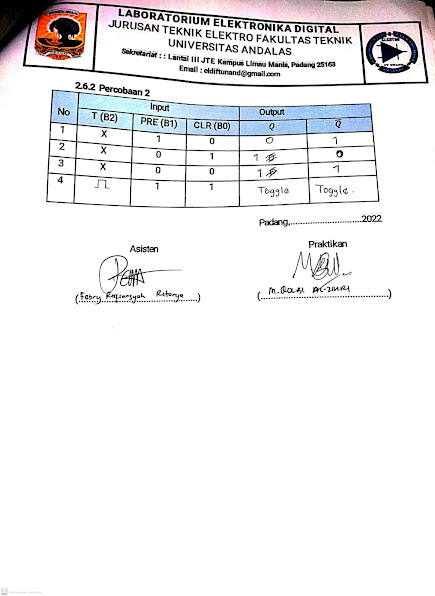

1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

Terdiri dari 2 yaitu, Modul D'Lorenzo dan Jumper

- Jumper

Kabel jumper adalah suatu istilah kabel yang ber-diameter kecil yang di dalam dunia elektronika digunakan untuk menghubungkan dua titik atau lebih dan dapat juga untuk menghubungkan 2 komponen elektronika. Kabel jumper jenis ini digunakan untuk koneksi male to male pada kedua ujung kabelnya

3. Rangkaian Percobaan [Kembali]

4. Prinsip Rangkaian

Pada percobaan T flip flop arus mengalir dari VCC ke JK. Arus mengalir dari VCC ke B2 dan ke CLK. Arus mengalir ke B0 dan tidak dilanjutkan karna terputus. Reset disambung B0 dan ke ground. Pada set diberi sinyal clock. J dan K merupakan aktif high, maka JK aktif karna berlogika 1. Reset merupakan aktif low, maka resen aktif karna berlogika 1 dan akan membuat output menjadi berlogika 0. Pada set diberi arus inpuls yg mana dalam keadaan toggle, yang membuat set menjadi aktif dan tidak aktif. Hal ini membuat output atau Q menjadi berubah ubah. Q' tidak berubah menjadi logika 0 saat set aktif karena reset sedang daalam keadaan aktif, jadi saling mempertahankan keadaannya.

5. Analisa

1. Apa yang terjadi jika B1 diganti CLK pada kondisi 2?

Jika B1 diganti dengan clock, maka ouput yang dihasilkan bernilai 1. Hal ini karena reset aktif yang membuat nilai ouput berlogika 1. Walaupun JK berlogika 1, output tidak dapat terjadi kondisi toggle, karena pin CLK dalam kondisi don't care. Jadi Output yang dihasilkan akan tetap berlogika 1.

2. Bandingkan hasil percobaan dengan teori!

Setelah dibandingkan percobaan dengan teori, bahwasanya yang dihasilkan pada percobaan sesuai dengan teori yang ada. Seperti saat RS berlogika 1 atau pada keadaan OFF, membuat ouputnya terjadi kondisi toggle. Saat set berlogika 0 atau aktif, maka akan membuat output menjadi berlogika 0. Saat reset berlogika 0 atau aktif, maka akan membuat output menjadi berlogika 0.

3. Apa fungsi masing-masing kaki Flip-Flop yang digunakan?

Kaki JK = sebagai input dari IC74LS112

Kaki CLK = Sebagai masukan untuk mengatur terjadinya toggle pada output.

Kaki R = sebagai pereset output yang membuat output berlogika 0

Kaki S = sebagai set output yang membuat output berlogika 1

Kaki Q = sebagai output dari IC

Kaki Q' = sebagai output yang hasilnya berlawanan dari Q

6. Video Pratikum [Kembali]

7. Link Download [Kembali]

Tidak ada komentar:

Posting Komentar